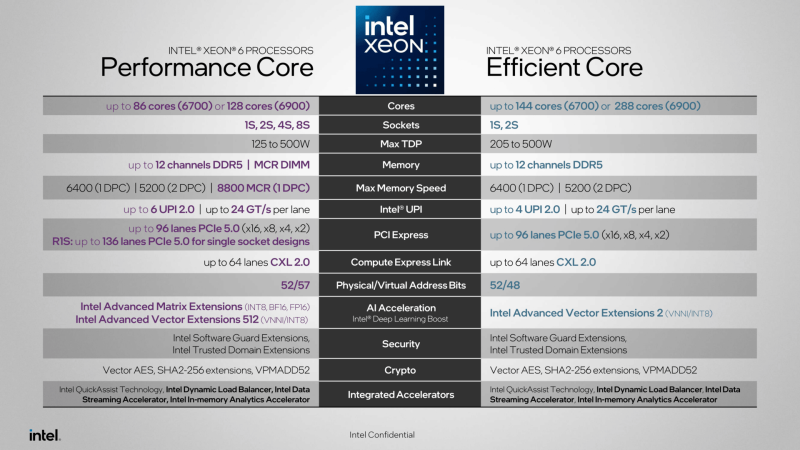

Intel Corporation, according to the ServeTheHome resource, is preparing special versions of Xeon 6 processors based on high-performance P-cores (Granite Rapids family). R1S products will receive an increased number of PCIe 5.0 lanes, but will be designed exclusively for single-socket systems.

In 1S, 2S, 4S and 8S variants, Xeon Granite Rapids chips offer up to 96 PCIe 5.0 lanes, up to 64 CXL 2.0 lanes and 12 RAM channels (DDR5-6400 and MCR-8800). The family includes models with 32, 44, 56, 72, 96, 120 and 128 Redwood Cove cores. They have SMT support and up to 504 MB L3 cache. The TDP value is up to 500 W.

Image Source: Intel

Xeon 6 R1S processors will reportedly support 136 PCIe 5.0 lanes. The number of computing cores, apparently, will not exceed 86. To install the chips, you will need a motherboard with an LGA-4710 connector. The TDP will not exceed 350 W. Among other things, support for up to 64 CXL 2.0 lines, as well as 8-channel DDR5-6400 memory or MCR DIMM is mentioned.

Image Source: Intel

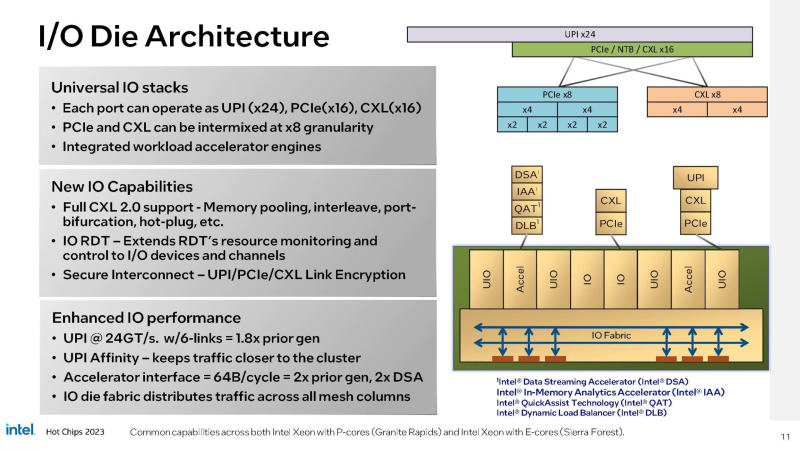

In the 1S configuration of the Xeon Granite Rapids chips, the IO tile’s universal input/output units (UIOs) can provide PCIe lanes instead of a UPI connection. In total, the IO tile has two I/O blocks for PCIe/CXL and four UIO blocks that can be used for PCIe, CXL and UPI. Thus, by eliminating UPI, Intel can offer additional PCIe lanes, bringing the number up to 136. This configuration is aimed at customers who do not need many compute cores, but want as many PCIe lanes as possible. A similar approach is used in AMD EPYC, where for communication between sockets it is also necessary to “take away” part of the PCIe lines.