Digital Autonomy with RISC-V in Europe (DARE), the largest chip project ever funded by the European Union, created to strengthen Europe’s technological sovereignty in high-performance computing (HPC) and artificial intelligence (AI), has officially launched the first phase of DARE SGA1, which has been funded with €240 million ($262 million), the project’s website reports. Europe and China are betting on RISC-V.

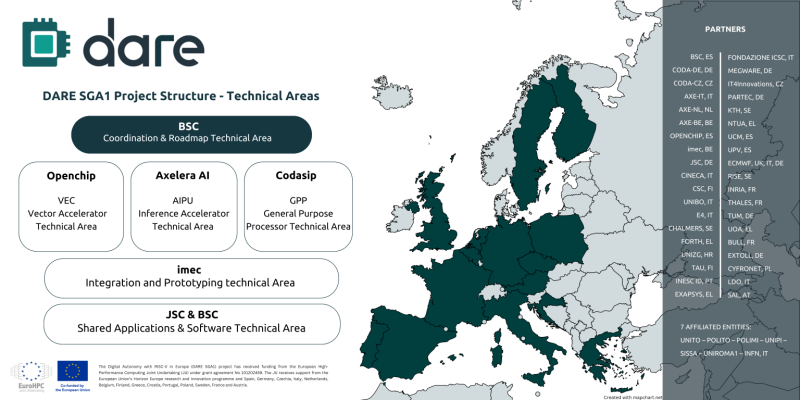

The initiative will be funded by 38 participants, including IT companies, research institutes and universities across Europe. The project is supported by the EuroHPC JU and coordinated by the Barcelona Supercomputing Centre (BSC-CNS), which has extensive experience in the development of RISC-V chips and supercomputing systems. Half of the investment in the DARE project will be provided by the European Commission through EuroHPC, and the other half will come directly from European partners, including €34 million from the Spanish Ministry of Science, Innovation and Universities.

The three-year DARE SGA1 is the first phase of a six-year DARE initiative. The goal is to create a fully independent European supercomputing hardware and software stack for HPC and AI, including chips, chiplet-based systems and software. The initiative aims to meet Europe’s strategic need for digital sovereignty and full control over critical computing infrastructure.

Image source: DARE

The DARE SGA1 project plans to develop three chiplets based on the RISC-V architecture, each of which will perform a critical function in HPC and AI computing:

- Vector accelerator (VEC) for HPC workloads and new converged HPC-AI applications. Barcelona-based chip developer Openchip will lead the development.

- AIPU, which is being developed to accelerate AI inference. Its creation has been entrusted to Dutch startup Axelera AI, which will be creating an AI chip using in-memory computing.

- A general-purpose processor (GPP) optimized for HPC workloads in European supercomputers. The development is led by German company Codasip. This processor will be configurable and adaptable for various HPC applications, including scientific computing, AI, and Big Data processing.

In addition to the companies named, imec and the JÜLICH Supercomputing Centre (JSC) are named as technical leaders and will drive forward key innovations within the project. In addition to coordinating efforts, BSC will also lead the development of plans and will be involved in the development of software and hardware solutions. The chiplets will be manufactured using CMOS technology using modern process technologies.

Axelera will receive up to €61 million in development funding, subject to various milestones being met over the next three years, Axelera CEO Fabrizio del Maffeo told EE Times. While Axelera’s current Metis AIPU chip is aimed at edge systems, del Maffeo said the chiplet-based product being developed under DARE is not a game-changer, but rather a scaling one.

Codasip announced the X730 64-bit RISC-V-based chip with CHERI architectural security last year. The company has raised $34.6 million in total funding over the past decade, according to The Next Platform, including funding from various EU initiatives, as well as a $2.5 million seed round in 2016 and a $10 million Series A round in 2018.